Delay time refers to the duration between an expected event and its actual occurrence, impacting system performance and efficiency in fields like telecommunications, computing, and transportation. Managing delay time effectively can improve response rates and user experience by minimizing waiting periods. Explore the rest of the article to understand how optimizing delay time can benefit your operations.

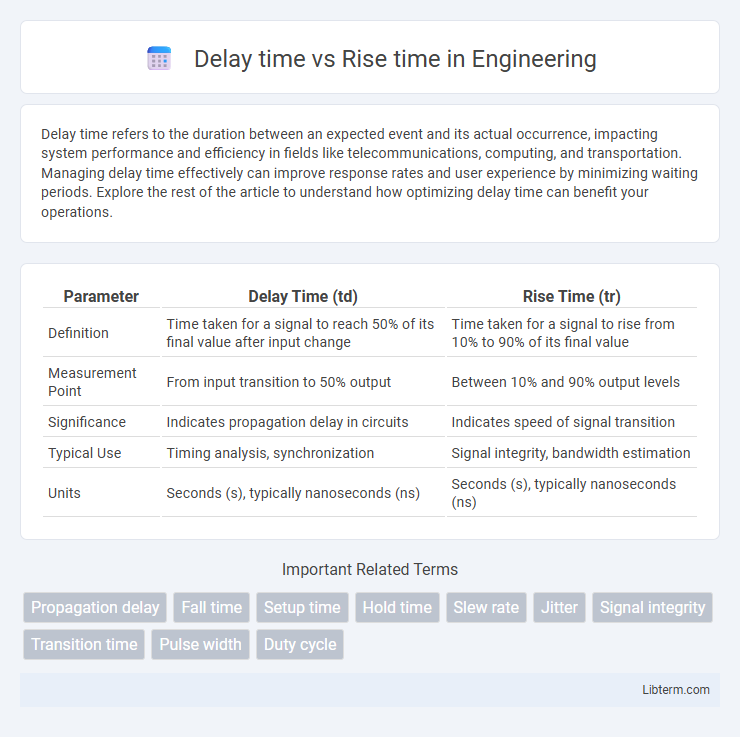

Table of Comparison

| Parameter | Delay Time (td) | Rise Time (tr) |

|---|---|---|

| Definition | Time taken for a signal to reach 50% of its final value after input change | Time taken for a signal to rise from 10% to 90% of its final value |

| Measurement Point | From input transition to 50% output | Between 10% and 90% output levels |

| Significance | Indicates propagation delay in circuits | Indicates speed of signal transition |

| Typical Use | Timing analysis, synchronization | Signal integrity, bandwidth estimation |

| Units | Seconds (s), typically nanoseconds (ns) | Seconds (s), typically nanoseconds (ns) |

Understanding Delay Time and Rise Time

Delay time refers to the interval between the application of an input signal and the beginning of the output response, indicating the system's initial reaction speed. Rise time measures the duration for the output to move from a specified low percentage (commonly 10%) to a high percentage (commonly 90%) of its final value, reflecting how quickly the system reaches near steady-state. Both delay time and rise time are critical parameters in characterizing the temporal performance of electronic circuits, digital systems, and control responses.

Key Differences Between Delay Time and Rise Time

Delay time measures the interval between the input signal application and the output beginning to respond, indicating when the output first starts changing. Rise time quantifies the duration required for the output to transition from a low to a high state, typically between 10% and 90% of the final value, reflecting the speed of signal change. Key differences include delay time representing the initial response latency, while rise time captures the rate at which the output completes its transition.

Importance of Delay Time in Electronic Circuits

Delay time, a critical parameter in electronic circuits, directly impacts the timing accuracy and overall speed of signal processing, influencing the synchronization between components in digital systems. Rise time, while important for defining the speed of signal transitions, is less crucial than delay time in determining propagation delays and ensuring reliable data transmission. Precise control of delay time improves circuit performance, minimizes timing errors, and enhances the stability of high-frequency and high-speed electronic devices.

The Role of Rise Time in Signal Integrity

Rise time is a critical parameter in signal integrity, influencing how quickly a signal transitions from low to high, which affects timing accuracy and noise margins. Short rise times minimize signal distortion and reduce the risk of timing errors in high-speed digital circuits. Understanding the interplay between rise time and delay time ensures optimal performance and reliability in signal transmission.

Factors Affecting Delay Time

Delay time is influenced by transistor switching characteristics, load capacitance, and supply voltage, which directly impact the speed of signal propagation in digital circuits. Higher load capacitance increases delay due to longer charging and discharging periods, while lower supply voltage slows transistor operation, extending delay time. Temperature variations also affect carrier mobility within semiconductor devices, thus altering the intrinsic delay properties.

Factors Influencing Rise Time

Rise time is primarily influenced by the bandwidth and capacitance of the system, where higher bandwidth reduces rise time while increased capacitance slows it. The input signal's slew rate and the load impedance also play critical roles, impacting how quickly the output can transition between voltage levels. Material properties and temperature variations further affect the rise time by altering the device's electrical characteristics and response speed.

Measurement Techniques for Delay Time

Measurement techniques for delay time primarily involve using high-speed oscilloscopes and time interval analyzers to capture the time difference between input signal changes and corresponding output responses. Precise triggering methods and sampling rates are crucial for accurately determining delay time in digital circuits, where delays can range from picoseconds to nanoseconds. Techniques such as Time Domain Reflectometry (TDR) and pulse generator synchronization enhance measurement accuracy by minimizing signal distortion and noise interference.

Methods to Measure Rise Time Accurately

Accurate measurement of rise time involves using high-bandwidth oscilloscopes and sampling techniques to capture the rapid voltage transitions with minimal distortion. Employing deconvolution methods and curve fitting algorithms reduces noise impact, enhancing the precision of rise time calculations. Calibration using reference signals and minimizing probe loading effects are essential to ensure the reliability of rise time measurement in high-speed circuits.

Applications Where Delay Time vs Rise Time Matters

Delay time and rise time critically influence high-speed digital circuits, where precise timing ensures signal integrity and synchronization across components such as microprocessors and memory modules. In communication systems, minimizing delay time enhances real-time data transmission, while controlled rise time reduces signal distortion and electromagnetic interference. Power electronics also rely on optimized delay and rise times to improve switch performance and reduce losses in devices like MOSFETs and IGBTs.

Optimizing Circuit Design for Better Delay and Rise Time

Optimizing circuit design for better delay and rise time involves selecting materials with low parasitic capacitance and resistance to minimize signal propagation delay and improve switching speed. Implementing proper transistor sizing and leveraging advanced fabrication technologies reduce the intrinsic delay, while careful layout strategies limit interconnect delays to achieve faster rise times. Accurate modeling and simulation tools enable designers to balance trade-offs between delay and rise time, ensuring enhanced overall circuit performance and reliability.

Delay time Infographic

libterm.com

libterm.com