Setup time represents the duration required to prepare equipment or processes before actual production begins, directly impacting overall efficiency and productivity. Minimizing setup time can lead to significant cost savings and faster turnaround, allowing your operations to run more smoothly. Discover strategies to reduce setup time and optimize your workflow in the rest of this article.

Table of Comparison

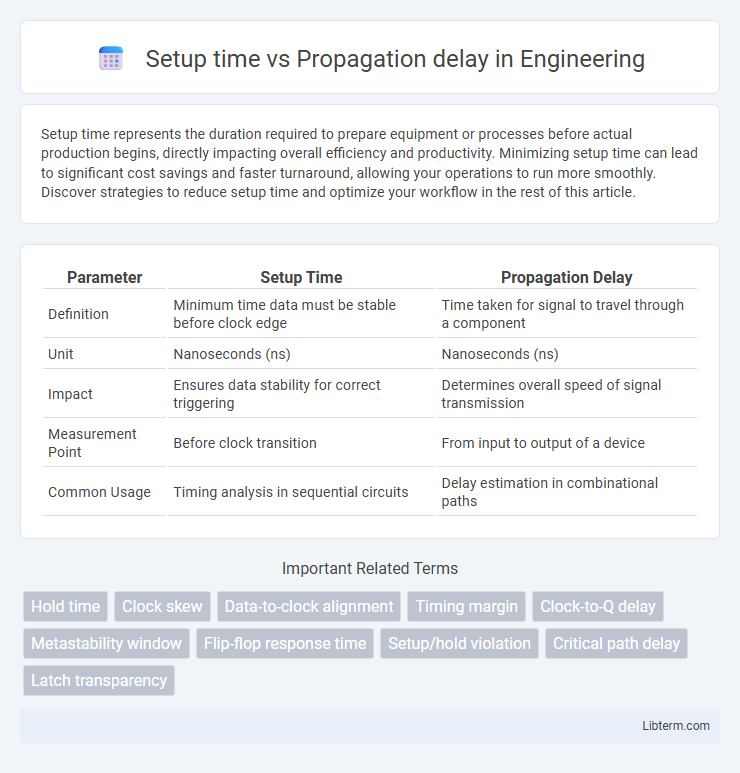

| Parameter | Setup Time | Propagation Delay |

|---|---|---|

| Definition | Minimum time data must be stable before clock edge | Time taken for signal to travel through a component |

| Unit | Nanoseconds (ns) | Nanoseconds (ns) |

| Impact | Ensures data stability for correct triggering | Determines overall speed of signal transmission |

| Measurement Point | Before clock transition | From input to output of a device |

| Common Usage | Timing analysis in sequential circuits | Delay estimation in combinational paths |

Understanding Setup Time: Definition and Importance

Setup time is the minimum duration before the clock edge during which the input signal must remain stable to ensure reliable data capture in sequential circuits. Violating setup time can lead to metastability, causing incorrect data to be latched and system malfunction. Understanding setup time is crucial for designing high-speed digital systems and optimizing timing analysis to guarantee data integrity and synchronous operation.

Exploring Propagation Delay in Digital Circuits

Propagation delay in digital circuits refers to the time it takes for a signal to travel from the input to the output of a logic gate, significantly impacting circuit performance and timing analysis. It is influenced by factors such as gate capacitance, resistance, and load, and plays a critical role in the maximum operating frequency of the circuit. Understanding propagation delay is essential for optimizing timing margins and ensuring reliable data transmission within synchronous systems.

Key Differences Between Setup Time and Propagation Delay

Setup time is the minimum interval before the clock edge during which input data must remain stable to ensure proper sampling in sequential circuits. Propagation delay refers to the time taken for a signal to travel through a combinational logic element and appear at the output after an input change. The key difference lies in setup time being a timing constraint for input data stability, while propagation delay is a measure of signal transmission latency within a circuit.

The Role of Setup Time in Flip-Flop Operation

Setup time is the minimum interval before the clock edge during which the data input of a flip-flop must remain stable to ensure correct data capture. Violating setup time can cause metastability or incorrect output, impacting overall circuit reliability. Proper adherence to setup time is critical for synchronous digital systems to maintain timing integrity and predictable operation.

How Propagation Delay Impacts Circuit Performance

Propagation delay directly affects circuit performance by determining the time it takes for a signal to travel through components, impacting overall speed and timing accuracy. Higher propagation delays can cause slower response times, limiting the maximum clock frequency and potentially leading to timing violations or data errors. Minimizing propagation delay is critical for high-speed circuits to ensure reliable synchronization and optimal throughput.

Factors Affecting Setup Time and Propagation Delay

Setup time is influenced by clock skew, data transition times, and the internal circuitry of the flip-flop, requiring data to be stable before the clock edge. Propagation delay depends on transistor switching speeds, capacitive loading, and the process technology, determining how quickly a signal travels through a gate or circuit. Both parameters are affected by temperature variations and supply voltage fluctuations, impacting overall chip performance and timing reliability.

Setup Time vs Propagation Delay: Timing Analysis

Setup time defines the minimum period before the clock edge during which data must remain stable to ensure correct capture, while propagation delay measures the time taken for a signal to travel through a combinational logic path. Accurate timing analysis compares setup time constraints to the total propagation delay to prevent data launch and capture timing violations in synchronous circuits. Ensuring the propagation delay remains shorter than the clock period minus setup time is critical for reliable flip-flop operation and overall system performance.

Common Timing Violations: Causes and Solutions

Setup time violations occur when data arrives later than the required setup time before the clock edge, causing incorrect data capture and system errors; this is often due to slow data paths or clock skew. Propagation delay violations happen when the signal takes longer than the clock period to propagate through logic, leading to timing mismatches and incorrect operation. Solutions include optimizing logic paths, using faster gates, reducing clock frequency, implementing proper clock tree synthesis, and employing timing analysis tools to identify and mitigate violations.

Optimizing Digital Systems for Minimal Setup Time and Propagation Delay

Optimizing digital systems for minimal setup time and propagation delay involves selecting high-speed flip-flops and optimizing clock distribution networks to ensure timely data capture and signal stability. Reducing setup time requires minimizing data path delays before the clock edge, while lowering propagation delay focuses on shortening the signal travel time through combinational logic. Employing advanced semiconductor technology and optimized circuit layout techniques significantly enhances overall system performance and timing reliability.

Real-World Examples: Setup Time and Propagation Delay in Practice

Setup time is critical in microprocessor design, ensuring that input signals stabilize before the clock edge to prevent data corruption; for instance, in modern CPUs like Intel's Core i9, setup times are minimized to achieve higher clock frequencies. Propagation delay represents the time taken for signals to travel through circuit elements, often limiting overall system speed, as seen in high-speed communication interfaces such as PCIe 5.0 where minimizing delay improves data throughput. Real-world electronic systems balance setup time and propagation delay by designing flip-flops and combinational logic with optimal timing margins, crucial in FPGA implementations and synchronous digital circuits.

Setup time Infographic

libterm.com

libterm.com